## **8 N-Channel Latchable Power MOSFET Array**

## **Ordering Information**

| V <sub>DD</sub> | R <sub>O(ON)</sub> | I <sub>O(ON)</sub> | I <sub>O(OFF)</sub> | Order Num | ber/Package |

|-----------------|--------------------|--------------------|---------------------|-----------|-------------|

| (max)           | (max)              | (min)              | (max)               | SO-16     | Die         |

| 320V            | 350Ω               | 25mA               | -1.0nA              | AN0332CG  | AN0332ND    |

<sup>\*</sup>Average current per channel, measured with all eight channels connected in parallel.

#### **Features**

|   | Low drain to source leakage                                   |

|---|---------------------------------------------------------------|

|   | Interfaces directly to TTL and CMOS logic                     |

|   | 8 independent channels                                        |

|   | Low crosstalk between channels                                |

|   | Low power dissipation                                         |

|   | Freedom from secondary breakdown                              |

|   | Serial data input                                             |

| П | On-chip decoder, latch with reset and write disable circuitry |

## **General Description**

The Supertex AN0332 is an 8 N-Channel 320V common source power MOSFET array with a CMOS 8 bit addressable latch. The outputs are guaranteed to have very low leakage current. The outputs are addressed by logic inputs A0, A1, and A2. The addressed and unaddressed output can be turned on or off by the data, reset, and write disable inputs.

The AN0332 is ideally suited for low leakage/high impedance measurements, providing excellent accuracy as well as resolution for automatic bare board test equipment and other applications.

## **Applications**

| High impedance/low leakage measurements for bare board testers |

|----------------------------------------------------------------|

| High voltage piezoelectric transducer drivers                  |

| High voltage electroluminescent panel drivers                  |

| High voltage electrostatic array drivers                       |

| General multi-channel driver arrays                            |

## Absolute Maximum Ratings<sup>1</sup>

| Output voltage, V <sub>DD</sub>         | 320V                     |

|-----------------------------------------|--------------------------|

| Logic supply voltage, V <sub>DD</sub>   | -0.5V to +15V            |

| Logic input levels, all inputs          | -0.5V to V <sub>DD</sub> |

| Operating and storage temperature range | -55°C to +150°C          |

| Soldering temperature <sup>2</sup>      | 300°C                    |

| Channel-to-channel crosstalk            | 10mV/V                   |

|                                         |                          |

#### Notes

- 1. All voltages are referenced to  $V_{\mbox{\scriptsize SS}}$ .

- 2. Distance of 1.6mm from case for 10 seconds.

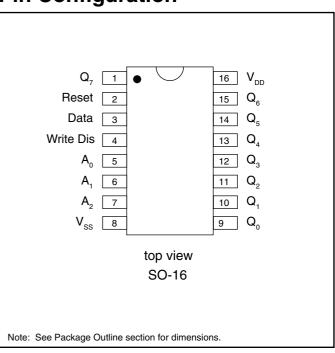

## **Pin Configuration**

## **Electrical Characteristics** (@ 25°C and V<sub>DD</sub> = 12V unless otherwise specified)

#### **DC Characteristics**

| Symbol              | Parameter                                          | Min | Тур  | Max  | Unit | Conditions                                                       |

|---------------------|----------------------------------------------------|-----|------|------|------|------------------------------------------------------------------|

| I <sub>O(OFF)</sub> | Off-State Output Current                           |     |      | 8.0  | nA   | V <sub>O</sub> = max. rating,<br>8 outputs connected in parallel |

| I <sub>O(ON)</sub>  | On-State Output Current                            | 25  |      |      | mA   | V <sub>O</sub> = 25V                                             |

| R <sub>O(ON)</sub>  | On-State Output Resistance                         |     |      | 350  | Ω    | I <sub>O</sub> = 10mA                                            |

| $\Delta R_{O(ON)}$  | Change in R <sub>O(ON)</sub> with High Temperature |     | 0.8  |      | %/°C | I <sub>O</sub> = 10mA                                            |

| I <sub>DDQ</sub>    | Quiescent Logic Supply Current                     |     | 0.05 | 16.5 | μΑ   |                                                                  |

| V <sub>IL</sub>     | Input Low Voltage                                  |     |      | 3.5  | V    |                                                                  |

| V <sub>IH</sub>     | Input High Voltage                                 | 12  |      |      | V    |                                                                  |

| I <sub>IN</sub>     | Input Current                                      |     |      | 1.0  | μΑ   |                                                                  |

Note:

# ristics - OBSOLETE -

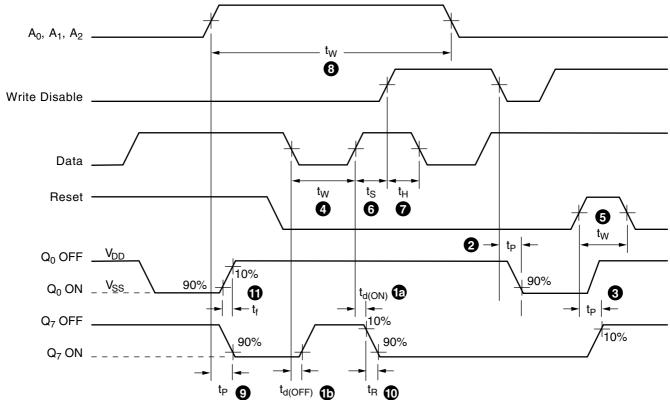

#### **AC Characteristics**

| Symbol                              | Parameter                                           | Min | Тур | Max | Unit | Fig. 1* | Conditions                                  |

|-------------------------------------|-----------------------------------------------------|-----|-----|-----|------|---------|---------------------------------------------|

| t <sub>D(ON)</sub>                  | Turn-On Delay Time                                  |     | 800 |     | ns   | 1a      |                                             |

| t <sub>D(OFF)</sub>                 | Turn-Off Delay Time                                 |     | 800 |     | ns   | 1b      |                                             |

| t <sub>r</sub>                      | Rise Time                                           |     | 200 |     | ns   | 10      |                                             |

| t <sub>f</sub>                      | Fall Time                                           |     | 200 |     | ns   | 11      |                                             |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Propagation Delay Time from Write Disable to Output |     | 87  |     | ns   | 2       | V <sub>O</sub> = 25V, I <sub>O</sub> = 10mA |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Propagation Delay Time from Reset to Output         |     | 87  |     | ns   | 3       |                                             |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Propagation Delay Time from Address to Output       |     | 107 |     | ns   | 9       |                                             |

| t <sub>W</sub>                      | Minimum Pulse Width – Data                          |     | 50  | 100 | ns   | 4       |                                             |

| t <sub>W</sub>                      | Minimum Pulse Width – Address                       |     | 100 | 200 | ns   | 8       |                                             |

| t <sub>W</sub>                      | Minimum Pulse Width – Reset                         |     | 40  | 75  | ns   | 5       |                                             |

| t <sub>S</sub>                      | Setup Time – Data to Write Disable                  | 50  |     |     | ns   | 6       |                                             |

| t <sub>H</sub>                      | Hold Time – Data to Write Disable`                  | 75  |     |     | ns   | 7       |                                             |

| C <sub>IN</sub>                     | Input capacitance - Any Input                       |     | 5.0 | 7.5 | pF   |         |                                             |

<sup>\*</sup>Refer to circled numbers on Timing Diagram (Figure 1).

Note:

<sup>1.</sup> All voltages are referenced to V<sub>ss</sub>.

<sup>1.</sup> All voltages are referenced to  $V_{\rm ss}$ .

## **Recommended Operating Conditions**

(For maximum reliability, nominal operating conditons should be selected so that operation is always within the following ranges.)

| Symbol          | Parameter                                    | V <sub>DD</sub> | Min                 | Max             | Unit |

|-----------------|----------------------------------------------|-----------------|---------------------|-----------------|------|

| $V_{DD}$        | Logic supply voltage                         |                 | 10.0                | 13.2            | V    |

| V <sub>O</sub>  | Output Voltage referenced to V <sub>SS</sub> |                 | 0                   | 320             | V    |

| V <sub>IH</sub> | Input High Voltage                           | 12V             | V <sub>DD</sub> - 2 | V <sub>DD</sub> | V    |

| V <sub>IL</sub> | Input Low Voltage                            | 12V             | 0                   | 2.0             | V    |

| T <sub>A</sub>  | Operating Free-Air Temperature               |                 | 0                   | 70              | °C   |

Note:

<sup>1.</sup> All voltages are referenced to V<sub>ss</sub>.

### **Mode Selection**

| Data   | Write Disable | Reset | Addressed Output | Unaddressed Outputs |

|--------|---------------|-------|------------------|---------------------|

| H<br>L | L             | L     | On<br>Off        | Holdspriv.          |

| H<br>L | Н             | L     | Holdspriv.       | Holdspriv.          |

| H<br>L | L             | Н     | On<br>Off        | Off                 |

| H<br>L | Н             | Н     | Off              | Off                 |

## **Timing Diagram**

## **Functional Block Diagram**

## OBSOLETE - $V_{DD}(+)$ Data ○ Write Disable <sup>○</sup> --○ **Q**<sub>7</sub> Latch --○ Q<sub>6</sub> Latch $\multimap Q_5$ Latch A<sub>0</sub> --○ Q<sub>4</sub> Latch 3:8 --○ Q<sub>3</sub> Decoder Latch A<sub>2</sub> ---○ Q<sub>2</sub> Latch --○ Q<sub>1</sub> Latch $\multimap Q_0$ Latch Reset O-

○ V<sub>SS</sub> (–)